嵌入式ARM时钟系统

一、时钟信号

时钟系统是嵌入式系统的核心部分。ARM时钟系统,通常指的是微控制器或微处理器中的时钟树(Clock Tree)及其管理单元。这些时钟系统为芯片内部的各个模块(如CPU、总线、外设等)提供时钟信号,使得它们能够同步工作。

1.1 时钟信号的本质

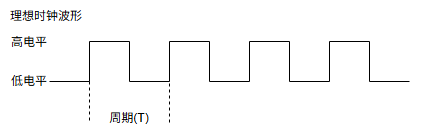

在电子世界中,时钟信号是一种周期性变化的电压信号,在高电平和低电平之间不断切换:

相关概念:

周期 (Period) :完成一次高低变化所需的时间。

单位:s(秒)

公式:周期(T) = 1 / 频率(f)

频率 (Frequency) :每秒钟时钟信号振荡的次数(每秒钟时钟信号变化的次数)。

单位:Hz(赫兹)、KHz(千赫)、MHz(兆赫)、GHz(吉赫)

换算:1GHz = 1000MHz = 1,000,000KHz = 1,000,000,000Hz

1MHz = 每秒振荡 1,000,000 次 ,即1秒内有1,000,000个时钟周期(T)。占空比 (Duty Cycle) :高电平时间占整个周期的比例。

公式:占空比 = 高电平时间 / 周期 × 100%

标准时钟:通常是50%占空比(高低电平各占一半)。

上升沿(Rising Edge)与下降沿(Falling Edge)

上升沿:时钟信号从低电平变为高电平的瞬间。

下降沿:时钟信号从高电平变为低电平的瞬间。

大多数数字电路在上升沿采样数据(同步逻辑)

1.2 时钟的作用和控制意义

数字电路由大量”触发器“(Flip-Flop)组成,触发器需要时钟边沿触发。寄存器(包括外设的寄存器)的读写、外设功能的运行,都依赖时钟信号。所以想要使用任何外设,必须先确保该外设的时钟已经开启。这就是为什么配置外设前,首先要配置时钟的原因。

时钟信号作为数字系统的”心跳”,其核心功能包括:

- 同步机制:确保数字电路各组件在特定时刻执行操作。

- 时序参考:为数据传输和状态转换提供时间基准,保证数据在正确的时刻被采样和传输。

- 功耗管理:通过时钟门控和频率调节实现能效优化。

- 性能调节:动态调整运算速度适应不同工作负载。

时钟控制的意义:

- 时钟频率越高,每秒处理次数越多,芯片性能越强,但功耗也越大。

- 不同外设需要不同的时钟频率。如果使用统一的高频,不仅浪费功耗,而且有些外设无法工作在高频率。

- 通过时钟门控开关,不用的外设可以关闭时钟,节省功耗。

二、时钟系统基础概念

2.1 时钟源 (Clock Source)

产生原始时钟信号的器件或电路。

常见类型:晶振、RC振荡器、外部时钟输入

晶体振荡器的基本工作原理是利用石英晶体的压电效应和谐振特性来产生恒定的频率。

(1) 外部晶体振荡器(Crystal Oscillator)

利用石英晶体的压电效应产生稳定频率振荡的器件。是高速外部时钟(HSE - High Speed External),常被标识为Xtal,Extenal Crystal Osillator。

常见频率:8MHz, 12MHz, 24MHz, 25MHz。

精度极高:±1050ppm (百万分之1050的误差)。对于 8MHz 晶振,误差约为 8MHz × 20ppm = 160Hz。

应用:主时钟源,需要高精度的场合。

(2) RC振荡器 (RC Oscillator)

RC振荡器是一种通过电阻(R)和电容(C)构成选频网络实现自激振荡的反馈型电路。是高速内部时钟(HSI - High Speed Internal),在芯片内部。

常见频率:4MHz, 8MHz, 16MHz。

精度较低:±1%~5% (受温度影响大)。

优点:无需外部元件,启动快,成本低。

应用:对精度要求不高的场合,或作为备用时钟。

(3) 低速外部晶振(LSE, Low Speed External)

频率:32.768kHz (= 2^15 Hz,便于分频得到1Hz)。

用途:实时时钟(RTC)、低功耗模式唤醒。

32768 ÷ 2^15 = 1Hz,经过15次分频后正好是1Hz(1秒)。

(4)低速RC振荡器 (LSI: Low Speed Internal)

频率:约32kHz~40kHz (精度较差)。

优点:功耗极低,始终可用。

用途:看门狗定时器、低功耗唤醒。

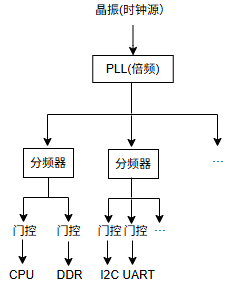

2.2 锁相环PLL- 时钟倍频器

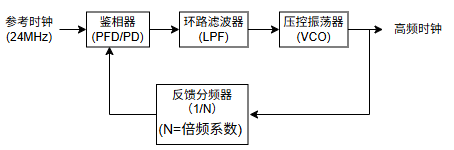

锁相环(PLL-Phase Locked Loop)是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。锁相环可用来从固定的低频信号生成稳定的输出高频信号等。

PLL的基本模型如下:

鉴相器(PFD,Phase Frequency Detector):比较输入信号和反馈信号的相位差,如果反馈信号慢了,输出”加速”信号,如果反馈信号快了,输出”减速”信号。

环路滤波器(LPF,Loop Filter):将鉴相器的脉冲信号转换为平滑的直流电压,过滤高频噪声,提高系统稳定性。

压控振荡器(VCO,Voltage Controlled Oscillator):根据输入电压产生对应频率的时钟。电压高→频率高,电压低→频率低,这是产生高频时钟的核心部件。

反馈分频器(Feedback Divider):将VCO输出的高频信号降低N倍,然后反馈给鉴相器进行比较。

倍频公式:输出频率 = 参考频率 × N

为什么需要PLL?

高频晶振价格昂贵,且电磁干扰大。晶振频率固定(如24MHz),但CPU需要几百MHz甚至GHz的高速时钟,外设也需要各种不同频率。较便宜的低频晶振通过PLL倍频可以获得各种高速频率。

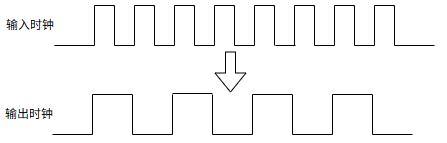

2.3 分频器(Divider / Prescaler)

分频器将高频时钟降低到合适低频率的电路。

原理:每N个输入时钟周期输出1个时钟周期。

二分频示例:

输出频率 = 输入频率 ÷ 2(频率变为一半,周期变为两倍)

不同外设需要不同频率,所以我们使用分频器可以将高频率时钟分频到合适的频率供不同外设使用。

2.4 时钟控制模块CCM

时钟控制模块CCM(Clock Controller Module)为设计中的各类模块生成并控制时钟,同时管理低功耗模式。该模块利用可用时钟源来生成时钟根。

- 时钟根生成逻辑(Clock root generation logic):该子模块提供用于控制大部分次级时钟源配置的寄存器,包括主时钟源选择与时钟分频器。时钟根(clock roots)是指供给内核、系统总线(AXI、AHB、IPG)及所有其他片上外设的各个独立时钟,其中包括串行时钟、波特率时钟和特殊功能时钟。大多数时钟根针对特定模块而设计。

- CCM 与 GPC、PMU 和 SRC 协同管理电源模式,即运行模式、等待模式和停止模式。外设时钟的门控在运行模式和等待模式下可编程配置。

CCM 管理以下频率调节流程:

- ARM 内核时钟——可通过切换锁相环源(PLL 时钟切换)或调整分频比,实现“动态”频率调整,且不会中断时钟信号。

- DDR 内存控制器时钟的切换。具体详见 MMDC 握手协议、自刷新及频率切换进入/退出流程。

- 外设根时钟——通过可编程分频器调节。分频系数可动态修改,且不会导致时钟丢失。

注意:

对于同步接口(如串行音频接口、视频与显示接口或通用串行接口(如 UART、CAN)),动态频率切换可能导致同步丢失,应避免此类操作。

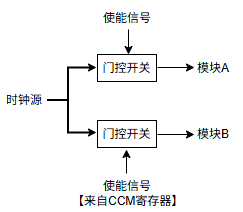

2.5 时钟门控(Clock Gating)

通过开关控制时钟是否传递到某个模块。

Low Power Clock Gating unit(LPCG) 从 CCM 接收原始时钟,并将其划分为供各个模块使用的时钟分支。这些时钟分支均为独立门控时钟。

门控时钟的使能信号可来自三个来源:

- 来自 CCM 的时钟使能信号:该信号根据系统所处的功耗模式生成。针对每种功耗模式,均可通过软件配置 CCM 中的 CGR 位进行定义。

- 来自对应功能模块的时钟使能信号:该信号由功能模块依据其内部逻辑产生。并非所有来自模块的使能信号都会被使用,且每个此类时钟使能信号均可通过 CCM 中的可编程位进行覆盖。

- 来自复位控制器(SRC)的时钟使能信号:该信号在复位流程中完成时钟使能。

不使用的外设关闭时钟,可以使功耗降低。动态时钟管理是低功耗设计的关键。

2.6 时钟域(Clock Domain)

时钟域是一组由CCM(时钟控制模块)中同一时钟控制信号驱动的功能模块集合。

通过对时钟域内的时钟进行门控(gating),无论是通过软件控制,还是与模块活动相关的硬件控制,均可对属于该时钟域的所有模块统一进行时钟门控 / 使能。因此,时钟域可实现对该域动态功耗的高效控制。

芯片被划分为多个时钟域,每个时钟域由LPCG(低功耗时钟门控)模块内对应的一组时钟门控单元控制。这使得 CCM/LPCG 能够对系统中每个时钟域进行独立的时钟使能与门控。

2.7 时钟树(Clock Tree)

时钟树是芯片内部一个专门设计的、用于将时钟信号从单一源点(如PLL锁相环)尽可能同时地传递到芯片所有时序元件(主要是寄存器和触发器)的分布式缓冲网络。其形状像一棵倒置的树,根是时钟源,枝叶终点是各个时序单元。

下面是一张时钟树示意图:

通过时钟树图,确定外设使用的是哪个时钟。

完